# PV-IPM Application Note

## **Index**

- 1. PV-IPM Features

- 2. Product Line-up

- 3. Term Explanation

- 4. Numbering System

- 5. Structure

- 6. Correct and Safety Use of Power Module

- 7. Reliability

- 7-1. Introduction

- 7-2. Basic Concepts of Semiconductor Device Reliability

- 7-3. Mitsubishi's Quality-Assurance Program

- 7-4. Reliability Testing

- 7-5. Failure Analysis

- 7-6. Derating and Reliability Projections

- 7-7. Conclusion

- 8. Installation of power Module

- 8-1. Installing Capacitor

- 8-2. Installation Hints

- 8-3. Thermal Impedance Considerations & Chip Layout

- 8-4. Coating Method of Thermal Grease (Example)

- 9. Using IPM

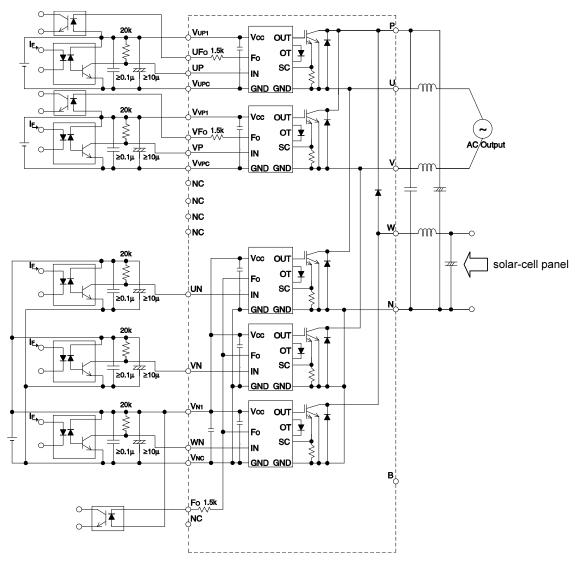

- 9-1. Applications of PV-IPM to Photo voltaic power generator

- 9-2. Interface of control side of IPM

- 9-3. Control Power supply of IPM

- 9-4. Fault Signal of IPM

- 9-5. Other notice of using IPM

- 10. Power Loss and Junction Temperature

- 11. Average Power Loss Simplified Calculation

- 12. Notice for safe Designs and when Using This Specification

## PV-IPM Feature, Product Line-up

#### 1.PV-IPM Feature

A small, decentralized power supplies such as the photovoltaic generation, wind power generation, and fuel cells are spreading from the rise of environmental problems. In addition, the spread of a domestic photovoltaic generation system and the fuel cell system will be expected in the future.

Because the voltage to which these generate electricity is DC, it is necessary to convert it into AC to use it at home.

The device for the DC-AC conversion is a power conditioner, and the power device is used for it. Efficiency is requested in the power conditioner, and the power device with low loss is requested. It is IPM for the photovoltaic generation to have satisfied such a demand.

#### **Features**

Integration of  $5^{th}$  generation trench chip (CSTBT $^{TM}$ ) achieves lower saturation voltage

Equipped with newly developed control IC

Using small package as same outer dimensions as L-series IPM

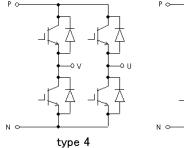

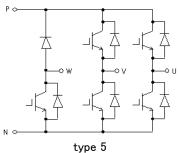

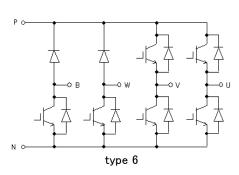

The single phase output inverter circuit and the chopper circuit are built into IPM

(type4: no chopper circuit, type5: chopper circuit\*1, type6: chopper circuit\*2)

#### **Applications**

Power conditioner for Photovoltaic generation and other small capacity generation system.

#### 2.Product Line-up

Single phase inverter circuit (type4)

Screw type package Pin type package

PM50B4LA060 PM75B4LA060 PM50B4LB060 PM75B4LB060

Single phase inverter circuit and 1 chopper circuit (type5)

Screw type package Pin type package

PM50B5LA060 PM75B5LA060 PM50B5LB060 PM75B5LB060

Single phase inverter circuit and 2 chopper circuit (type6)

Screw type package Pin type package

PM50B6LA060 PM75B6LA060 PM50B6LB060 PM75B6LB060

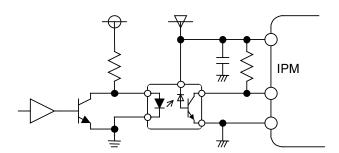

#### Internal circuit

## Package

Pin type package

## Term Explanation

## 3. Term Explanation

## General 1

| Symbol          |                                   | Definition                                                                      |

|-----------------|-----------------------------------|---------------------------------------------------------------------------------|

| IGBT            | Insulated Gate Bipolar Transistor |                                                                                 |

| FWDi            | Free Wheeling Diode               | Anti-parallel to the IGBT                                                       |

| IPM             | Intelligent Power Module          |                                                                                 |

| tdead           | Dead Time                         | Low side turn-off to high Side turn-on & High Side turn-off to low side turn-on |

| IPM Motor       | Interior Permanent Magnet Motor   |                                                                                 |

| (PC)            | Photo-Coupler                     |                                                                                 |

| PC              | Programable Controller            |                                                                                 |

| CMR             | Common Mode Noise Reduction       | The maximum rise ratio of common mode voltage                                   |

| CM <sub>H</sub> |                                   | The maximum rise ratio of common mode voltage at the specific high level        |

| CM <sub>L</sub> |                                   | The maximum rise ratio of common mode voltage at the specific low level         |

| CTR             | Current Transfer Ratio            | the ratio of the output current to the input current                            |

## General 2

| Symbol         | Parameter           | Definition                                                     |

|----------------|---------------------|----------------------------------------------------------------|

| Ta             | Ambient Temperature | Atmosphere temperature without being subject to thermal source |

| T <sub>c</sub> | Case Temperature    | Case temperature measured at specified point                   |

## Absolute maximum Ratings

| Symbol           | Parameter                          | Definition                                                                                                                    |  |

|------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CES</sub> | Collector-Emitter Blocking Voltage | Maximum Off-state collector-emitter voltage with gate-emitter shorted                                                         |  |

| Ic               | Continuous Collector Current       | Maximum collector current – DC                                                                                                |  |

| I <sub>CM</sub>  | Peak Collector Current Repetitive  | Peak collector current, Tj≤150°C                                                                                              |  |

| Ι <sub>Ε</sub>   | Continuous Diode Current           | Maximum diode current – DC                                                                                                    |  |

| I <sub>EM</sub>  | Peak Diode Current Repetitive      | Diode peak current, Tj≤150°C                                                                                                  |  |

| Pc               | Power Dissipation                  | Maximum power dissipation, per device, T <sub>C</sub> =25°C                                                                   |  |

| $T_{j}$          | Junction Temperature               | Allowable range of IGBT junction temperature during operation                                                                 |  |

| T <sub>stg</sub> | Storage Temperature                | Allowable range of temperature within which the module may be stored or transported without being subject to electrical load. |  |

| V <sub>iso</sub> | Isolation Voltage                  | Minimum RMS isolation voltage capability applied electric terminal to base plate, 1 minute duration                           |  |

| -                | Mounting Torque                    | Allowable tightening torque for terminal and mounting screws                                                                  |  |

lephaI<sub>E</sub> and I<sub>F</sub> are using by the difference of the connection and so on like the following figure.

## **Electrical Characteristics**

| Symbol               | Parameter                            | Definition                                                                                                                                                                                                                                |

|----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>CES</sub>     | Collector-Emitter Leakage<br>Current | $I_C$ at $V_{CE} = V_{CES}$ , $V_{GE} = 0V$                                                                                                                                                                                               |

| $V_{\text{CE(sat)}}$ | Collector-Emitter Saturation Voltage | $V_{CE}$ at $I_C$ = rated $I_C$ and $V_{GE}$ = 15V                                                                                                                                                                                        |

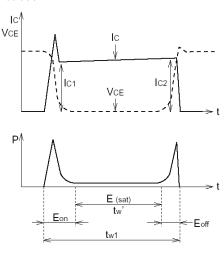

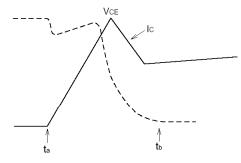

| tc(on)               | Turn-on Delay Time                   | Time from I <sub>C</sub> =10V to V <sub>CE</sub> =10% of final value                                                                                                                                                                      |

| tc(off)              | Turn-off Delay Time                  | Time from V <sub>CE</sub> =10% of final value to I <sub>C</sub> =10% of final value                                                                                                                                                       |

| E <sub>on</sub>      | Turn-on Switching loss               | Energy dissipated inside the IGBT during the turn-on of a single collector current pulse. Integral time starts from the 10% rise point of the collector current and ends at the 10% of the collector-emitter voltage point.               |

| E <sub>off</sub>     | Turn-off Switching loss              | Energy dissipated inside the IGBT during the turn-off of a single collector current pulse. Integral time starts from the 10% rise point of the collector-emitter voltage and ends at the specified low collector current point, x% of Ic. |

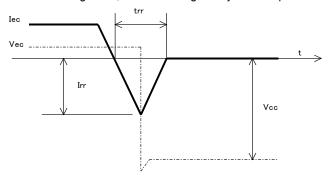

| t <sub>rr</sub>      | Diode Reverse Recovery Time          | Time from I <sub>C</sub> =0A to projection of zero I <sub>C</sub> from Irr and $0.5 \times$ Irr points with I <sub>E</sub> = rated I <sub>C</sub> .                                                                                       |

| $V_{EC}$             | Forward Voltage Drop of Diode        | V <sub>EC</sub> at -I <sub>C</sub> = rated Ic                                                                                                                                                                                             |

| R <sub>th</sub>      | Thermal Resistance                   | The rise of junction temperature per unit of power applied for a given time period                                                                                                                                                        |

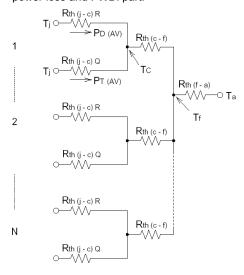

| R <sub>th(j-c)</sub> | Thermal Resistance, Junction to Case | I <sub>C</sub> conducting to establish thermal equilibrium                                                                                                                                                                                |

| R <sub>th(c-f)</sub> | Thermal Resistance, Case to Fin      | I <sub>C</sub> conducting to establish thermal equilibrium lubricated                                                                                                                                                                     |

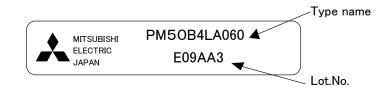

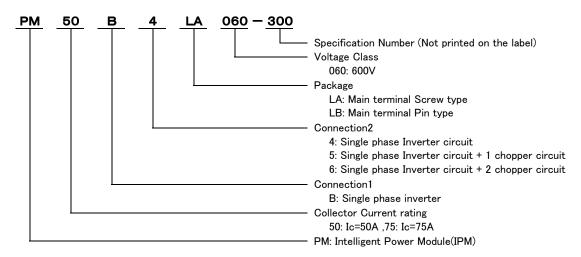

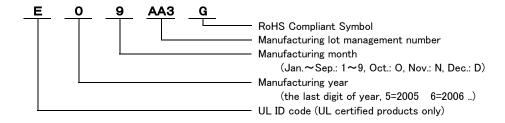

## **Numbering System**

## 4. Numbering System

Label)

## Type Name)

## Lot Number)

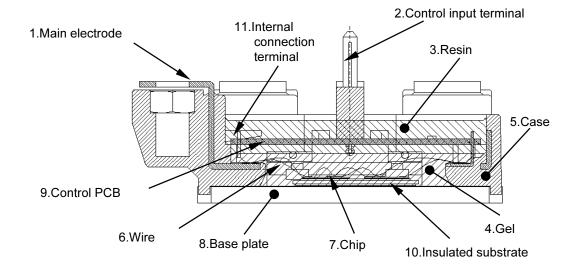

## 5. Structure

## ex.) Screw type Package

|    | Part                         | Quality of the material   | UL Flame class |

|----|------------------------------|---------------------------|----------------|

| 1  | Main electrode               | Copper plated with nickel |                |

| 2  | Control input terminal       | Brass plated with gold    |                |

|    |                              | PPS resin                 | UL 94-V0       |

| 3  | Resin                        | Ероху                     | UL 94-V0       |

| 4  | Gel                          | Silicone                  |                |

| 5  | Case                         | PPS resin                 | UL 94-V0       |

| 6  | Wire                         | Aluminum                  |                |

| 7  | Chip                         | Silicon                   |                |

| 8  | Base plate                   | Copper                    |                |

| 9  | Control PCB                  | Glass epoxy               | UL 94-V0       |

| 10 | Insulated substrate          | Ceramic*                  |                |

| 11 | Internal connection terminal | Copper plated with nickel |                |

## Note of Insulated substrate

\* : All about its structure, material, thickness, and manufacturer is the same as S-series IPM. S-series IPM has UL(Underwriters Laboratories Inc) Yellow Card #80276 (file. #80271).

6

## Correct and Safety Use of Power Module

## 6. Correct and Safety Use of Power Module

Unsuitable operation (such as electrical, mechanical stress and so on) may lead to damage of power modules. Please pay attention to the following descriptions and use Mitsubishi Electric's IGBT modules according to the guidance.

|                                        | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| During Transit                         | <ul> <li>Keep shipping cartons right side up. If stress is applied by either placing a carton upside down or by leaning a box against something, terminals can be bent and/or resin packages can be damaged.</li> <li>Tossing or dropping of a carton may damage devices inside.</li> <li>If a device gets wet with water, malfunctioning and failure may result. Special care should be taken during rain or snow to prevent the devices from getting wet.</li> </ul> |

| Storage                                | • The temperature and humidity of the storage place should be 5~35°C and 45~75% respectively. The performance and reliability of devices may be jeopardized if devices are stored in an environment far above or below the range indicated above.                                                                                                                                                                                                                      |

| Prolonged Storage                      | When storing devices more than one year, dehumidifying measures should be provided for the storage place. When using devices after a long period of storage, make sure to check the exterior of the devices is free from scratches, dirt, rust, and so on.                                                                                                                                                                                                             |

| Operating Environment Flame Resistance | <ul> <li>Devices should not be exposed to water, organic solvents, corrosive gases, explosive gases, fine particles, or corrosive agents, since any of those can lead to a serious accident.</li> <li>Although the epoxy resin and case materials are in conformity with UL 94-V0 standards, it should be</li> </ul>                                                                                                                                                   |

| Anti-electrostatic                     | noted that those are not non-flammable.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Measures                               | (1) Precautions against the device rupture caused by static electricity  Static electricity of human bodies and cartons and/or excessive voltage applied across the gate to emitter may damage and rupture devices. The basis of anti-electro static build-up and quick dissipation of the charged electricity.                                                                                                                                                        |

|                                        | * Containers that are susceptible to static electricity should not be used for transit nor for storage.  * Gate to emitter should be always shorted with a carbon cloth or the like until right before a module is used. Never touch the gate terminals with bare hands.                                                                                                                                                                                               |

| Anti-electrostatic<br>Measures         | * Always ground the equipment and your body during installation (after removing a carbon cloth or the like. It is advisable to cover the workstation and it's surrounding floor with conductive mats and ground them.                                                                                                                                                                                                                                                  |

|                                        | * It should be noted that devices may get damaged by the static electricity charged to a printed circuit board if the gate to emitter of the circuit board is open.  * Use soldering irons with grounded tips.                                                                                                                                                                                                                                                         |

|                                        | (2) Precautions when the gate to emitter is open  * Voltage should not be applied across the collector to emitter when the gate to emitter is open.  * The gate to emitter should be shorted before removing a device from a unit.                                                                                                                                                                                                                                     |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## Correct and Safety Use of Power Module

# **⚠** Cautions

#### Mounting

When mounting a module on a heat sink, a device could get damage or degrade if a sudden torque ("one side tightening") is applied at only one mounting terminal, since stress is applied on a ceramic plate and silicon chips inside the module. Shown in Fig.1 is the recommended torquing order for mounting screws.

(a) Two-Point Mounting Type

Temporary tightening ①→②

Final tightening ②→①

\*: Temporary tightening torque should be set at 20~30% of maximum rating.

Also, care must be taken to achieve maximum contact (i.e. minimum contact thermal resistance) for the best heat dissipation.)

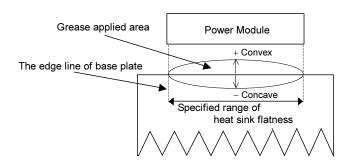

The flatness of a heat sink where a module is mounted (ref.Fig.2) should be as follows. Also, the surface finish should be less than Rz12s.

Copper base plate module: $-100\mu m\sim +100\mu m$

Thermal compound with good thermal conductivity should be applied evenly about Aluminum base plate modules: $-100\mu m\sim +200\mu m$  on the contact surface of a module and a heat sink.

Heat sink flatness: Less than ± 20 micrometers on a length of 100mm

/Less than 10 micrometers of roughness

Thermal grease thickness:  $+50\sim+100\mu m$

Grease on the contact surface prevents the corrosion of the contact surface. However, use the kind of grease that has a stable characteristic over the whole operating temperature range and does not change its properties for several years.

A torque wrench shall be used in tightening mounting screws and tighten screws to the specified torque. Excessive torquing may result in damage or degradation of a device.

Fig.2 Heat Sink Flatness

## Reliability

#### 7. Reliability

#### 7-1. Introduction

It has only been somewhat over 30 years since semiconductor devices such rectifier diodes. as thyristors. and gained widespread transistors acceptance for use in industrial machinery consumer appliances, but during that period the reliability standards for these devices have made rapid advances.

In equipment where high reliability is a must, failure rate of the semiconductor devices must range from 10 to 100 FIT (1 FIT=10<sup>-9</sup>/hours). Of course, to achieve such reliability in the equipment itself, not only must each individual device be reliable, but also it is also extremely important to match the specific characteristics of the device with its application within the piece of equipment. In fact, information obtained in field studies show that for semiconductor devices manufactured using identical procedures, failure rates in the field could vary by a factor of 10 depending simply on how the device was used.

The following information covers device reliability with regards to how a device is used. An introductory discussion is also presented on quality-control procedures, and some examples of reliability testing data are given.

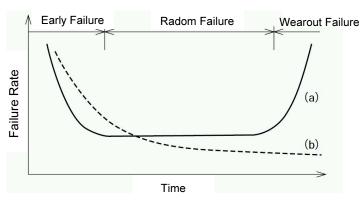

Fig.7.1 Failure Rate Versus Time

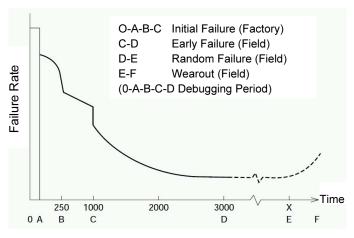

Fig.7.2 Semiconductor Device Failure Rate Versus Time

## 7-2. Basic Concepts of Semiconductor Device Reliability

#### 7-2-1. Semiconductor Device Failure Rate Varied with The Lapse of Time

The failure rate of devices used in an average piece of equipment can be expressed by using the bathtub curve shown in Fig.7.1, line (a). Taken from the standpoint of time, device failures can be classified as an early failure, random failure and wear out failure period. Three points must be considered regarding the service life of a device; early and random failures rate, and lifetime before wear out.

But the failure rate of semiconductors is illustrated by line (b) in the graph, where failure rate is shown to gradually diminish as a factor of time. In other words, a notable feature of semiconductor devices is that the longer a particular device has been used, the more stable it will be. Viewed from a different perspective, even though random failure rate has been reduced to virtual stability, the failure distribution pattern shows early failures to still be prevalent. As shown by Fig.7.2 where failure rate versus time is given for an actual device, the highest failure rate occurs immediately after manufacture, but the process of ageing and debugging gradually lowers this failure rate.

The next step is with the user, who assembles, adjusts, and takes the device aging. Failure rates continue to decline during this period also. Generally, the rate for major defect during this period drops to less than 0.1%, and if this rate is exceeded by a substantial margin, one must look for a fault in the circuit design, assembly procedure, or the device itself. Unless the problem is found and corrected, frequent field failures will be the likely result. In most cases, the field failure rate can be correlated to major defect during this period, so this is an important aspect of device reliability.

Upon transferring the equipment to field service, the stress level is reduced further, with a corresponding drop in failure rates. Failure rates normally range from several FIT to several hundred FIT during this period.

On the other hand, the user must design greater margins. For example, diodes and thyristors should be operated at  $50 \sim 60\%$  of their maximum voltage ratings or lesser, and junction temperatures should not exceed  $70 \sim 80\%$  of maximum rating. It is also important to remember that a device must be in working harmony with other components in the circuit for maximum reliability standards can be assured.

When designing a piece of equipment for reliable service, device selection must be considered from a standpoint of performance, reliability, and economy. Since it is not easy to achieve high performance/reliability and economy at the same time, a balance must be struck on the side of practical value. In other words, device selection should be based on the user's expectations for the machine he is designing.

## 7-2-2. Power Module Failure Reason

After a piece of equipment has been assembled and adjusted, or has been placed in field service, failed devices that are returned to the factory are analyzed to determine the cause of failure. This procedure is intended to determine whether the problem lays with the device itself, or the manner in which it was used. This section will list potential reasons of failure.

| · Good ———            | Device Unmatch for Circuit or Usage Condition                                       |

|-----------------------|-------------------------------------------------------------------------------------|

| Usage Condition——     | Over voltage                                                                        |

| J                     | ├── V <sub>CE</sub> Over voltage (Collector-Emitter)                                |

|                       | Switching Surge                                                                     |

|                       | Bus Bar Voltage Rise                                                                |

|                       | Abnormal Control Signal                                                             |

|                       | │ │ │ │ │ │ │ Interfered Noise (Lightning Surge)                                    |

|                       | Inappropriate Measurement                                                           |

|                       | V <sub>GE</sub> Over voltage (Gate-Emitter)                                         |

|                       | ├ Static Electricity                                                                |

|                       | Abnormal Gate Drive Circuit                                                         |

|                       | - Gate Oscillation                                                                  |

|                       | High Voltage Applied                                                                |

|                       | └ Interfered Surge                                                                  |

|                       | Over Temperature (Over Current, Over Load)                                          |

|                       | ├── Inappropriate Thermal Design                                                    |

|                       | ├── Short Arms (Not Enough Dead-Time, False Turn-on )                               |

|                       | ├─ Over Current                                                                     |

|                       | ├── Under Gate Drive Voltage                                                        |

|                       | ├─ Gate Circuit Open                                                                |

|                       | ├── Abnormal Switching Frequency Increase                                           |

|                       | ├── Abnormal Switching Frequency Decrease                                           |

|                       | ├── Inappropriate Thermal System                                                    |

|                       | └── Bonding Surface Fatigue                                                         |

|                       | Insulation Failure (Ceramic Crack, Internal Solder Melting)                         |

|                       | ├── Heat Sink Mounting Failure (Over Stress)                                        |

|                       | └── Over Voltage                                                                    |

| Power Device Defect — | IGBT Chip Manufacture Defect                                                        |

|                       | Pattern Defect                                                                      |

|                       | Surface Fault (Impurity ion)                                                        |

|                       | └─ Module Manufacture Defect                                                        |

|                       | ├── Wire Bonding Fault                                                              |

|                       | Connection Fault Between Insulation Base Plate and Module Base Plate (Solder, etc.) |

|                       | ├── Internal Electrode Solder Fault                                                 |

|                       | └─ Metalization Fault                                                               |

Operation life is dependent on the internal wire bonding, thermal fatigue between insulation base-plate and module base-plate. The thermal fatigue will be described in the next page.

## 7-2-3. Thermal Fatigue of Power Module

## 7-2-3-1 Operating Temperature Pattern

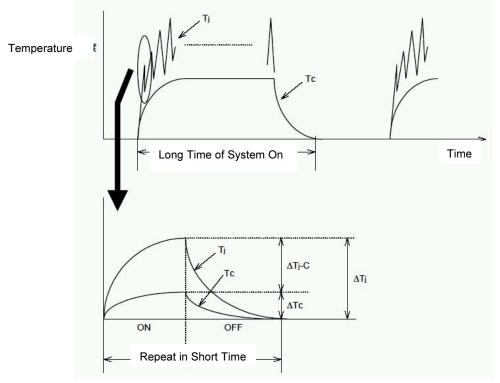

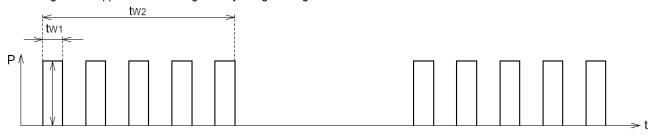

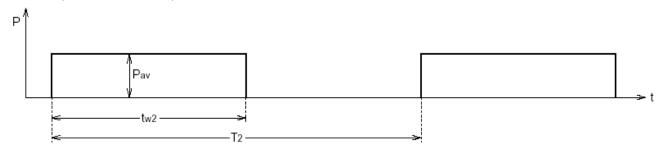

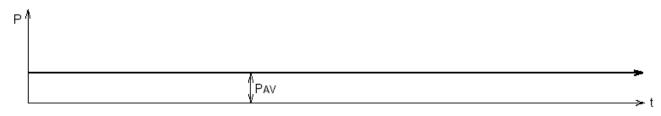

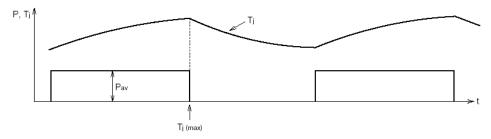

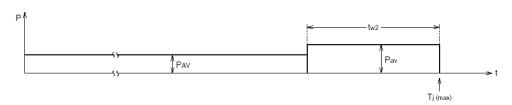

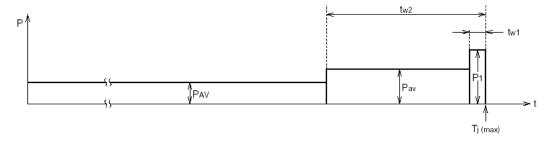

The operating temperature pattern of power module is displayed in Fig.7.3. It is important to consider two patterns that are independent each other in thermal fatigue life of power module.

- ■Operation Mode 1

- Power cycle life is called when change of case temperature is small, but frequent change of junction temperature occurs.

- ■Operation Mode 2

The other one is thermal cycle life when comparatively slow change of temperature occurs by start and stop of the system.

Fig.7.3 Operating Temperature Pattern

#### 7-2-3-2. Power Cycle Failure Mechanism

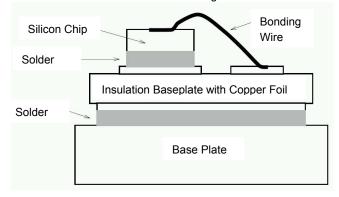

Fig.7.4 shows the typical construction of power module. When junction temperature of power module is changed, stress strain between aluminum wire and silicon chip, and between silicon chip and insulation substrate occurs due to the difference of coefficient of linear expansion. If this stress is supplied repetitively, thermal fatigue for the junction becomes failure.

For inverter use, power cycle life is a necessary concern, which should be given during designing system. An example is given in Fig.7.5. The failure mode is that the crack of bonding surface makes progress by stress due to the difference of linear expansion between aluminum wire and silicone chip and finally lead to the peel failure mode.

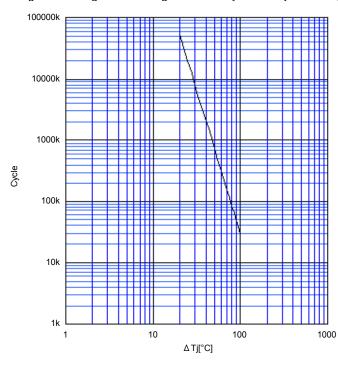

A power cycle testing result of Mitsubishi Electric's module is shown in Fig.7.6.

Insulation substrate aluminum wire crack aluminum wire crack silicon chip

Fig.7.5 Bonding Surface Fatigue Caused by Power Cycle Testing

Fig.7.6 Power Cycle Curve

#### 7-3. Mitsubishi's Quality-Assurance Program

One of the basic goals of Mitsubishi Electric is to offer our customers quality products. As a consequence, product quality, price, timely delivery, and service are equally important aspects deserving an equal amount of attention. Still, product quality must stand above all others from a standpoint of customer confidence.

Quality standards in the semiconductor industry are extremely high; production of wafers is a carefully controlled, precision process, and assembly processes are done under microscopes to assure that there are no sacrifices made in technology, or in quality.

The following subsections outline the quality-assurance programs Mitsubishi Electric uses in its mass-production.

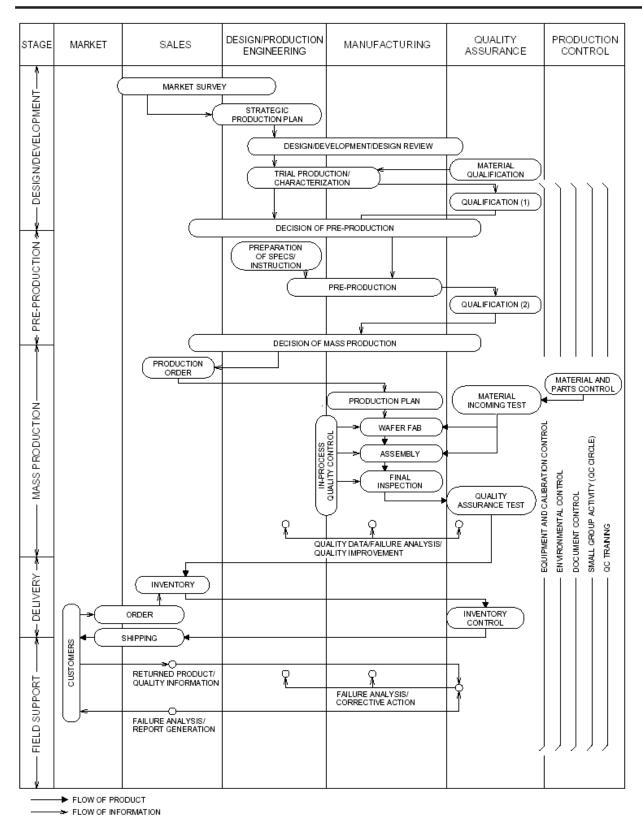

#### 7.3.1 The Path to a Mass-Production Device

From research prototype, through mass-production, a serial type tests are run at each stage to assure performance and reliability of the ultimate product. At the same time, the design drawings are also closely checked. The path from the research stage to mass-production is shown in the flow chart of Fig.7.7 The subsections that follow briefly describe the reliability tests used to check for device reliability.

#### 7.3.2 Environmental Controls

The semiconductor industry as a whole recognizes the affect environmental factors have on product quality, and rigorous standards have been established regarding the control of dust, humidity, and temperature in manufacturing facilities. The same level of standards is also used for the various gases, and the water used in the manufacturing process.

### 7.3.3 Periodic Inspection and Maintenance of Manufacturing Equipment and Instrumentation

The various equipment and measuring instruments used in semiconductor production are an extremely important element of the total process. It is therefore imperative that a periodic program be implemented to inspect and adjust these components so that optimum precision standards are maintained, and to forestall any interruptions in the production process.

#### 7.3.4 Quality-Control of Materials Purchases

Materials are subjected to rigorous acceptance tests using equipment such as spectrometers, helium leak detectors, etc. Before placing full orders, thorough sample testing is done, and all problem areas are worked out before making an official decision. Quality-control procedures at the supplier's plant are also considered in any procurement decision.

#### 7.3.5 Control of the Manufacturing Process

Various measures have been taken to control the elements that have a decisive influence on the quality of the product. Measuring instruments are used to monitor water purity, atmospheric conditions, furnace temperatures, gas flow, and other factors. Check-sheet inspections are made, and recorders keep automatic records. These records are carefully correlated with the records kept on matters such as diffusion depth and surface density to establish proper working conditions.

#### 7.3.6 In-Process and Final Inspections

The goals of the in-process and final inspections are twofold: the first is to assure product quality from the standpoint of outer appearance, dimensions, structural integrity, and mechanical and electrical characteristics. The second is to feed this information back upline to improve quality, and to reduce variations in future batches.

In-process inspections are intended to check the wafer and assembly processes, and serve two purposes; one being self-imposed checks on the production process, the other for use as a quality-control tool. As its name implies, production personnel to correct deficiencies they clearly recognize use the self-imposed check, and emphasis is placed on points that are difficult to detect in completed devices. After the device is completed, it is subjected to the final inspection and the quality-assurance inspection. The final inspection is run on all devices, and consists of testing electrical characteristics and outer appearance. Quality-assurance personnel assume the role of the end user, and inspect samples for correct electrical characteristics, outer appearance, and reliability before devices are packed in storage.

The flow chart for the quality-assurance program covered in the above is noted in Fig.7.9.

#### 7.3.7 Quality Information

Mainly the quality assurance division compiles various kinds of quality information such as inspection results and customer-supplied information. They are quickly fed back to related divisions including the production division for maintenance and improvement of quality.

In addition, we employ computer-based, streamlined, and effective quality control systems in order to modernize the information management.

## Reliability

Fig.7.7 Flow Chart of Quality Assurance Program

## 7-4. Reliability Testing

#### 7-4-1 Reliability Testing Procedures

High reliability standards are assured with Mitsubishi semiconductor devices through the rigorous quality-control inspections, which the devices are subjected to in the design and manufacturing stages, and through the quality-assurance inspections run on each production lot. Numerous reliability tests have been implemented in order to maintain this standard of reliability.

This section provides an overview of the reliability testing of thyristor devices. Test parameters are shown in Table 7.1, and as noted, conform to the procedures specified by the Japan Electronics and Information Technology Association (JEITA) handbook. (Related standards: International Electro technical Commission (IEC))

#### 7-4-2 Results of Reliability Test of IGBT Module

Table 7.2 lists the results of the reliability tests performed on PM75B6LA060, a resin sealed type with current rating up to 75A to date. Failure criterion information is noted in Table 7.3.

Table 7.1. Mitsubishi Power Module Reliability Testing

|               | Test Parameter                |         | od        | Test Conditions                                             |  |

|---------------|-------------------------------|---------|-----------|-------------------------------------------------------------|--|

|               | Thermal Shock                 | ED-4701 | B-141     | [Condition A] 100°C: 5 min, 0°C: 5 minutes, 10 cycles       |  |

|               | Temperature Cycling           | "       | B-131     | Tstg min 60 min∼Tstg max 60 min, 10 cycles                  |  |

| Environmental | Vibration                     | "       | A-121     | [Condition B] 10~500Hz/15 minute, 98.1m/s <sup>2</sup> , 6h |  |

| Test          | Robustness of Termination     | "       | A-111- I  | 9.8~40N, 10±1s                                              |  |

| rest          | Solder Heat Resistance        | "       | A-132     | [Condition A] 260±5°C, 10±1s, Rosin flux used               |  |

|               | Solderability                 | "       | A-131     | [Condition A] 235±5°C, 5±0.5s, Rosin flux used              |  |

| Mou           | Mounting Torque               | "       | A-112- II | M5:1.96~3.5N·m, 10±1s                                       |  |

|               | High Temperature Storage      | "       | B-111     | Ta=Tstg max, 1000 h                                         |  |

|               | Low Temperature Storage       | "       | B-112     | Ta=Tstg min, 1000 h                                         |  |

| Endurance     | Wetproof                      | "       | B-121     | [Condition B] Ta=60°C, RH=90%, 1000h                        |  |

| Test          | Intermittent Current Flow     | "       | _         | ΔTc=50°C(ΔTc=100°C), 5000 cycles                            |  |

|               | High Temperature Reverse Bias | "       | _         | Ta=Tstg max, VCE=85%VCES, VGE=0V, 1000h                     |  |

|               | High Temperature Gate Bias    | "       | _         | Ta=Tstg max, VCE=20V, VGE=0V, 1000h                         |  |

<sup>\*:</sup>Environmental and resistance testing conforms to standards specified in JEITA ED-4701 for discrete semiconductor devices. Table7.2. PM75B6LA060 Reliability Test Results

|               | Test Parameter                | Test Met | hod       | Test Conditions                                                            | No of<br>Samples | No of<br>Failures |

|---------------|-------------------------------|----------|-----------|----------------------------------------------------------------------------|------------------|-------------------|

|               | Thermal Shock                 | ED-4701  | B-141     | [Condition A] 100°C(5min), 0°C(5min), 10 cycles                            | 5                | 0                 |

|               | Temperature Cycling           |          | B-131     | -40°C(60 min)~125°C(60 min), 10 cycles                                     | 5                | 0                 |

| Environmental | Vibration                     |          | A-121     | [Condition B] 10~500Hz / 15 min, 98.1m/s <sup>2</sup> , 6h                 | 5                | 0                 |

| Test          | Robustness of Termination     |          | A-111- I  | 9.8N, 10±1 s                                                               | 5                | 0                 |

|               | Mounting Torque               |          | A-112- II | Mounting Screws:M5, 3.5N·m, 10±1 s Main Terminal Screws:M5, 3.5N·m, 10±1 s | 5                | 0                 |

|               | High Temperature Storage      |          | B-111     | Ta=125°C, 1000h                                                            | 5                | 0                 |

| Endurance     | Low Temperature Storage       |          | B-112     | Ta=-40°C, 1000h                                                            | 5                | 0                 |

| Test          | Wetproof                      |          | B-121     | Ta=60°C, RH=90%, 1000 h                                                    |                  | 0                 |

| rest          | Intermittent Current Flow     | _        |           | Ta=50~100°C, , 5000h                                                       | 5                | 0                 |

|               | High Temperature Reverse Bias | _        |           | Ta=125°C, VCES=510V, 1000h                                                 | 5                | 0                 |

Talbe7.3. PM75B6LA060 Failure Criterion

| Test Parameter                  | Test Conditions | Failure (            | Note        |      |  |

|---------------------------------|-----------------|----------------------|-------------|------|--|

| rest Parameter                  | rest Conditions | Lower Limit          | Upper Limit | Note |  |

| ICES                            | VCE=600V, VD=0V | _                    | U.S.L×2.0   |      |  |

| VCE(sat)                        | IC=75A, VD=15V  | _                    | U.S.L×1.2   |      |  |

| VEC                             | -IC=75A, VD=0V  | _                    | U.S.L×1.2   |      |  |

| SC                              | VD=15V,VCIN=0V  | L.S.L×0.9            | ı           |      |  |

| UV                              | trip            | L.S.L × 0.9          | I           |      |  |

| Electrical Stress AC2500V 1 min |                 | Insulation breakdown |             |      |  |

Note. U.S.L: Upper Specification Limit / L.S.L: Lower Specification Limit

## Reliability

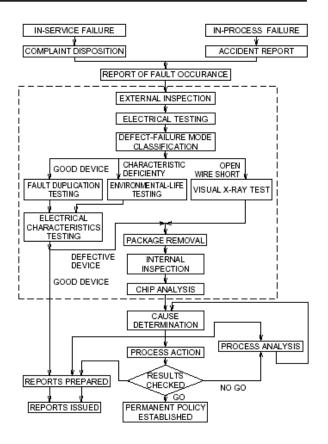

#### 7-5. Failure Analysis

Failure analysis is one of the sources of information used in maintaining, and making improvements in standards of quality and reliability. Failure analysis procedures are performed on failed devices at all stages of their life cycle, ranging from the development state to failure while in use. Failure analysis procedures are generally divided into area of external inspections, electrical testing, internal inspections, and chip analysis. The flow chart for these procedures is shown in Fig.7.8, while Table 7.4 lists the nature of the tests.

The results of the various reliability and failure analysis tests reveal the failure mode and mechanism, and this information is fed back to the process technology and manufacturing personnel so that they can take the appropriate measures to improve the final product.

#### 7-6. Derating and Reliability Projections

The degree of reliability for a semiconductor device varies considerably depending on usage and environmental conditions. Design standards, the method of manufacture, and quality-control procedures also play a role in establishing the intrinsic reliability for semiconductors. Correlating device derating with reliability is also not an easy task. Please refer to Mitsubishi device reliability handbook for more information in detail.

http://www.semicon.melco.co.jp/confidence/index.html

Fig.7.8 Failure Analysis Procedure

Table 7.4. Failure analysis inspections and equipment used

| Category                              | Inspection Items                                                                                                                                                                | Equipment                                                           |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| External Inspection                   | Condition of leads, plating, soldering, and welds     Packaging defect     Solderability                                                                                        | Stereoscopic microscope<br>Metallurgy microscope                    |

| Electrical Characteristics<br>Testing | Static electrical characteristics, voltage and temperature margins, checking for broken bond wire, wire     Internal wiring                                                     | Oscilloscope Curve tracer Characteristics tester X-ray equipment    |

| Internal Inspection                   | O Device removed from package and chip surface observed for defects O Electrical characteristic check using microprobe O Check for hot spots and other abnormalities            | Metallurgy microscope<br>microprobe<br>Scanning electron microscope |

| Chip Analysis                         | O Analysis techniques used to supplement chip surface observation in internal inspection     Cross-section of chip observed for analyzing oxide film, diffusion and metallizing | X-ray micro-analyzer<br>Infrared micro-scanner<br>Spectrum analyzer |

#### 7-7. Conclusion

The above is a simple introduction to general ideas about reliability, reliability tests, and derating and forcasting of reliability of high power semiconductor, which are semiconductor devices for electric power. As explained above, it is vital for higher reliability in practical use of semiconductor devices to understand their features and select those, which are suitable for equipment and sets. It is also important to design semiconductor devices with some allowance to improve reliability, fully taking their derating into consideration in relation to operating and environmental conditions.

Other essential things to do are to "debug" equipment and sets, and to analyze data obtained in fabrication process and actual operation to feed them back to design and fabrication stages. To improve the reliability by design of high power semiconductor requires considerations on many issues as described above. Utilize the semiconductor devices successfully with the utmost care with comprehensive understanding of their quality, reliability, and economy.

## Installation of power Module

#### 8. Installation of power Module

### 8-1 Installing Capacitor

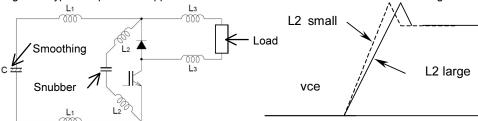

During switching, voltage is induced in power circuit stray inductance by the high di/dt of the main current. This voltage can appear on the IPM and cause damage. In order to avoid this problem, guidelines that should be followed in designing the circuit layout are:

- ① Located the smoothing capacitor as close as possible to the IPM

- ② Use ceramic capacitor near the IPM to bypass high frequency current

- 3 Adopt low impedance electrolytic capacitor as smoothing capacitor

- 4 Use snubber circuit to absorb surge voltage

- ⑤ Decrease switching speed in order to lower di/dt.

② and ⑤ are the most effective to reduce surge voltage. The stray inductance of snubber circuit generally is not considered to avoid complicating the circuit. In addition, combination of ②, ④, ⑤ is needed since there is a limit on the length of wiring. The bypass capacitor of approach ② act as a snubber when oscillation is occurring.

- L1: Stray inductance between the electrolytic capacitor and the IPM.

- L2: Stray inductance between the filter capacitor and the driver.

- L3: Stray inductance between the load and the power circuit's output stage

### 8-2 Installation Hints

When mounting IPM on a heat-sink, uneven mounting can cause the modules ceramic isolation to crack.

To achieve the best thermal radiation effect, the bigger the contact area is, the smaller the thermal resistance is Heat-sink should have a surface finish in range of Rz6  $\sim$  Rz12, curvature within 100 $\mu$ m.

Uniform coating of thermal grease between the module and heat-sink can prevent corrosion of contact parts. Select a compound, which has stable characteristics over the whole operating temperature range and does not change its properties over the life of the equipment.

Use a uniform coating of thermal interface compound. The thickness of thermal grease should be ranked in 100~200µm according to the surface finish.

Mounting screws should be tightened by using a torque wrench to the prescribed torque in progressive stages in a cross pattern. As mentioned before, over torque terminal or mounting screws may result in damage of IPM.

When an electric driver is used, thermal grease with low viscosity is recommended and extra grease must be extruded before final tightening screws.

- \* For the recommended torque order for mounting screws referring to "Installation Method" in the section of "Correct and Safety Use of Power Module"

- Note) Maximum torque specifications are provided in device data sheets. The type and quantity of thermal compounds having an effect on the thermal resistance are determined by consideration of both thermal grease and heat-sink. Typical value given in datasheet is measured by using thermal grease produced by Shin-Etsu Chemical Co.,Ltd. (G-746, which has not issued in Shin-Etsu's publications, is almost the same as G-747.)

## Installation of power Module

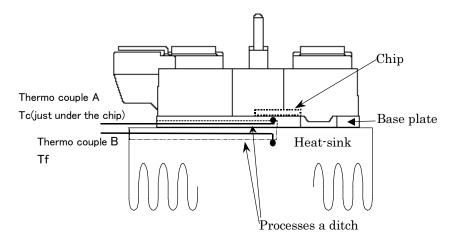

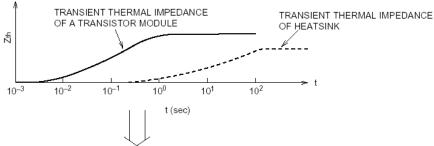

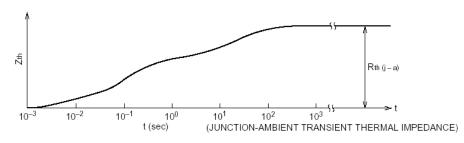

## 8-3 Thermal Impedance Considerations & Chip Layout

The junction to case thermal resistance  $R_{th(j-c)}$  and the case to heat-sink thermal resistance  $R_{th(c-f)}$  are given in datasheet. The case temperature has been measured at the just under the chip.

The case temperature measurement point of various products is shown in Table 3. It is measured by uniform  $100\mu m^2 200\mu m$  coating of thermal grease with thermal conductivity of  $0.92W/m^2$  between the module and heat-sink. A Thermo-couple is used to measure the temperature of case and heat-sink at the same point shown in the following tables. (0.8 $\phi$  3mm depth, 0.3 $\phi$  thermo-couple)

#### ·Note

Table 3:Thermal resistance and chip layout of PV-IPM Thermal resistance

|                | Inverter   |           | Chopper   |                     |              | contact thermal resistance |

|----------------|------------|-----------|-----------|---------------------|--------------|----------------------------|

|                | Just under | the chip  | Jı        | Just under the chip |              |                            |

| Type Name      | IGBT-chip  | FWDi-chip | IGBT-chip | FWDi(P)-chip        | FWDi(N)-chip |                            |

|                | Rth(j-c)Q  | Rth(j-c)  | Rth(j-c)Q | Rth(j-c)            | Rth(j-c)     | Rth(c-f)                   |

| PM50B4LA/LB060 | 0.95       | 1.61      | _         | _                   | _            | 0.038                      |

| PM50B5LA/LB060 | 0.95       | 1.61      | 0.95      | 0.95                | 1.61         | 0.038                      |

| PM50B6LA/LB060 | 0.95       | 1.61      | 0.95      | 0.95                | 1.61         | 0.038                      |

| PM50B4LA/LB060 | 0.32       | 0.53      | _         | _                   | _            | 0.038                      |

| PM50B5LA/LB060 | 0.32       | 0.53      | 0.32      | 0.33                | 0.53         | 0.038                      |

| PM50B6LA/LB060 | 0.32       | 0.53      | 0.32      | 0.33                | 0.53         | 0.038                      |

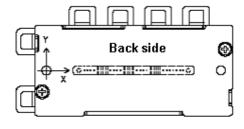

Unit(mm) Chip Layout UP VΡ WP BP UN VN WN BN IGBT FWDi IGBT FWDi **FWD**i **FWDi** IGBT FWDi IGBT FWDi IGBT FWDi IGBT FWDi Χ 31.1 30.6 61.0 60.5 38.2 40.7 52.9 50.4 PM50B4LA/LB060 -10.0 -10.0 0.2 -2.2-2.28.0 0.2 8.0 \_ 32.7 32.2 62.8 63.3 82.9 38.8 39.3 53.0 52.5 75.6 75.1 PM50B5LA/LB060 -10.0 -0.2-8.8 -2.0 -8.4 0.8 8.0 3.8 -2.8 3.8 -2.8 32.7 32.2 62.8 63.3 82.9 21.8 38.8 39.3 53.0 52.5 75.6 75.1 18.1 25.9 Χ PM50B6LA/LB060 -10.0 -2.0 -0.2-8.8 -8.4 6.8 0.8 8.0 3.8 -2.8 3.8 -2.8-10.0 -8.4 30.4 30.4 61.7 61.7 39.7 39.7 52.4 52.4 PM75B4LA/LB060 -8.3 -0.8 -8.3 -0.8 6.3 \_ -1.26.3 -1.233.6 31.2 66.0 66.0 85.8 40.5 41.6 56.2 56.2 76.3 76.3 PM75B5LA/LB060 -7.54.5 -8.6 0.6 -3.1 0.8 0.0 2.7 -5.5 2.7 -6.5 Χ 33.6 31.2 66.0 66.0 85.8 22.7 40.5 41.6 56.2 56.2 76.3 76.3 18.7 26.1 PM75B6LA/LB060 -3.1 -7.5 4.5 -8.6 0.6 7.2 0.8 0.0 2.7 -5.5 2.7 -6.5 -10.1 -9.0

<sup>\*</sup>The thermal impedance depends on the material, area and thickness of heat-sink. The smaller the area and the thinner the heat-sink is, the lower the impedance is for the same material.

<sup>\*</sup>The type and quantity of thermal compounds can affect the thermal resistance.

## Installation of power Module

1) Screw type

2) Pin type

## 8-4 Coating Method of Thermal Grease (Example)

The coating method of thermal grease is introduced in this section. The thermal grease is called as grease in the following.

- ① Preparations: power module, grease, scraper or roller, electronic mass meter and gloves

- ② Relationship between the coating amount and thickness is,

Thickness of grease =

$$\frac{\text{amount of grease [g]}}{\text{base area of module [cm}^2] \times \text{density of grease [g/cm}^3]}$$

The recommended thickness of grease is  $100\mu m\sim 200\mu m$ .

The amount of grease can be obtained as the following example.

For example : For case with size of  $110 \times 89$  (PM100CSD060), the amount of Shin-Etsu Chemical Co.,Ltd. grease G-746 can be calculated through the equation below.

$$100 \sim 200 \mu \text{m} = \frac{\text{amount of grease[g]}}{97.9[\text{cm}^2] \times 2.66[\text{g/cm}^3]}$$

∴The amount needed is \= 2.6~5.2 [g]

- 3 Measure the mass of module

- Measure the grease with the same amount as calculated

- © Coating the module base uniformly by using scraper or roller

- Mask print of grease.

Finally it is fulfilled to uniformly cover thermal grease on the module base with specified thickness.

Table 4 Thermal Compounds

| Manufacturer                 | Туре                           | Note                    |

|------------------------------|--------------------------------|-------------------------|

| Shin-Etsu Chemical Co., Ltd. | KS-609, G-747, else            |                         |

| GE Toshiba Silicones         | YG6260                         |                         |

| ALCAN                        | UNIVERSAL<br>JOINTING-COMPOUND | For non-insulation type |

For more information, please refer to manufacturers.

## 9. Using IPM

## 9-1 Applications of PV-IPM to Photo voltaic power generator

(ex. PM50B5LA/LB060, PM75B5LA/LB060)

Notes for stable and safe operation ;

- Design the PCB pattern to minimize wiring length between photo-coupler and IPM's input terminal, and also to minimize the stray capacity between the input and output wirings of photo -coupler.

- Connect low impedance capacitor between the Vcc and GND terminal of each fast switching photo -coupler.

- Fast switching photo -couplers : tpLH, tpHL $\leq$ 0.8  $\mu$  s, Use High CMR type.

- Slow switching photo -coupler : CTR>100%

- Use 3 isolated control power supplies (V<sub>D</sub>). Also, care should be taken to minimize the instantaneous voltage charge of the power supply.

- Make inductance of DC bus line as small as possible, and minimize surge voltage using snubber capacitor between P and N terminal.

- Use line noise filter capacitor (ex. 4.7nF) between each input AC line and ground to reject common

-mode noise from AC line and improve noise immunity of the system.

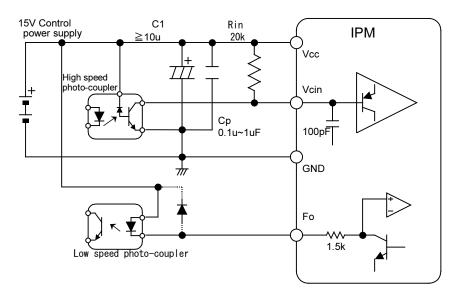

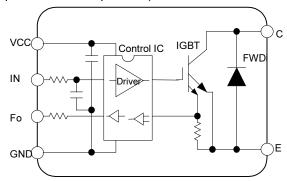

#### 9-2 Interface of control side of IPM

IPM (Intelligent Power Modules) is easy to operate. The integrated drive and protection circuits require only an isolated power supply and a low level on/off control signal. A fault output is provided for monitoring the operation of the module internal protection circuits.

(1) Circuit and circuit constant of the IPM interface circuit

The parts of connecting IPM and controller (CPU) are required to use following parts.

3 Condenser (Ceramic condenser for the ripple removal

and electrolytic condenser for the power stabilization)

Fo terminal 4 Low(high) speed photo-coupler

Control power supply

⑤ The mutually insulated stabilized power source of +15 V

(The negative power as it uses in IGBT-MOD is unnecessary.)

Example of constant value of the IPM interface circuit

| Symbol | Name                | Recommend Value | Note                                                                   |

|--------|---------------------|-----------------|------------------------------------------------------------------------|

| - ,    | INAITIE             | Necommend value | 11212                                                                  |

| Rin    | Pull-up resistor    | 20kΩ            | All input terminal (include Br)                                        |

| C1     | Smoothing capacitor | ≥ 10uF          | It is necessary that the charge and discharge electric current and the |

| Ср     | Bypass condenser    | 0.1 ~ 1uF       | dv/dt electric current to IPM(IGBT gate) can be sufficiently absorbed. |

| PC     | Photo-coupler       | High CMR, CTR   | ex.) PS9613                                                            |

### (2) IPM Internal circuit diagram and interface circuit

## (3) IPM Control terminals

The IGBT power switches in the IPM are controlled by a low level input signal. The active low control input will keep the power devices off when it is held high. Typically the input pin of the IPM is pulled high with a resistor connected to the positive side of the control power supply. An ON signal is then generated by pulling the control input low.

The recommended value of the pull-up resistor is 20 k $\Omega$  but it can be smaller for the noise countermeasure and so on. However, if the pull-up resistor is set too small, it will affect the lifetime of the photo-coupler, please confirm the characteristics with lifetime and so on in the photo-coupler manufacturer.

## **Using IPM**

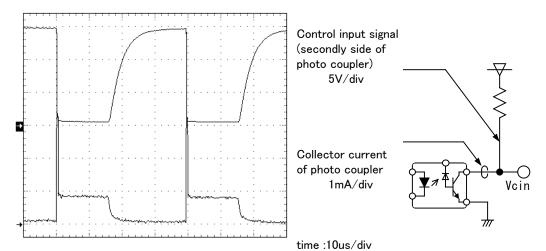

The inside of the control input terminal is connected to the comparator and is with high impedance. When IPM (IGBT) is turn-off, the output impedance of the photo-coupler becomes high. Total impedance of the circuit which connect the interface circuit is equal to a resistance of about  $20K\Omega$ .

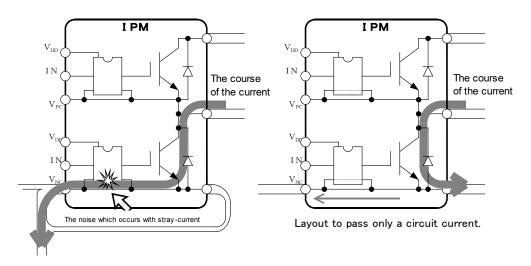

The most important consideration in interface circuit design is layout. Shielding and careful routing of printed circuit wiring is necessary in order to avoid coupling of dv/dt noise into control circuits. Parasitic capacitance between high side interface circuits, high and low side interface circuits, or primary and secondary sides of the isolating devices can cause noise problems. Careful layout of control power supply and isolating circuit wiring is necessary. In layout, it is important not to make wiring of the photo-coupler primary side and secondly side cross each other. Also, pattern should be made shortest and not to be crowded around and the magnetic field make the inside of the current-loop not cross. Place condenser with good frequency response between the power - GND of the photo coupler.

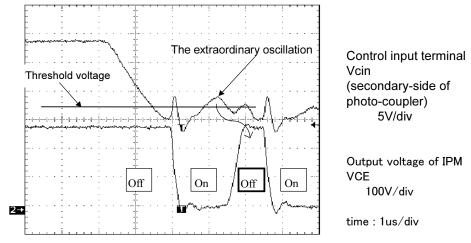

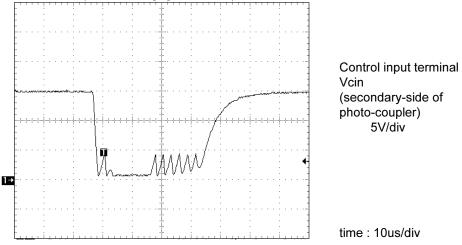

Depending on the pattern layout, sometimes a ringing as shown below occurs. In this case, the output current of the photo-coupler doesn't change so much than the corrugation at normal.

However, the ringing problem increases the IPM switching loss, results possibly the IPM heat destruction. It is necessary to check in design.

Fig.9.1 The example of the oscillation waveform A of the photo-coupler

In the following example, the oscillation happens at the timing of both after on and off. When the oscillation after turn off continues over the dead time, it falls in the period when the opposite arm becomes on then cause an arm short failure. The protection circuit works and IPM outputs Fo. This phenomenon sometimes happens under the condition of no-load. It is easily confused with the malfunction on the side of IPM and the cause investigation takes time. As a countermeasure, reducing the power supply impedance of the photo-coupler and the photo-coupler use by IPM compatible is effective.

Fig.9.2 The example of the oscillation waveform B of the photo-coupler

#### (4) Fo terminal of IPM

Fo is the output which shows the abnormal condition of IPM.

The extraordinary modes are overheating(OT), load ( the arm ) short circuit(SC), and control supply under voltage(UV). Fo does not distinguish these kinds of failures.

The fault output is open collector type with its maximum sink current internally limited. When a fault condition occurs the open collector device turns on allowing the fault terminal to sink current from the positive side of the control supply. The inside of the Fo terminal is the open-collector composition which connected resistance  $(1.5K\Omega)$  in series.

#### Note)

If Fo is not used, the malfunction being able to be detected on the side of the system, passing away, it isn't possible to do a protection-coordination with the system. For example, if Fo on the P-side is not used, then a earth-short failure will not be able to protect in the system, and the earth-short occurs continuously. Because IPM sometimes destroys when this condition continues, it is recommended to use all Fo terminals.

Fo terminal is connected with the comparator input circuit inside IPM. When leave this terminal open, there is possibility that the noise invades from this terminal and cause malfunctions of the circuit inside IPM. In this case, inserting a high frequency type condenser of about  $0.1~\mu F$  between the Fo terminal and GND is effective. Also, when not use Fo, in order not to undergo influence by the noise, connect it to 15 V control source.

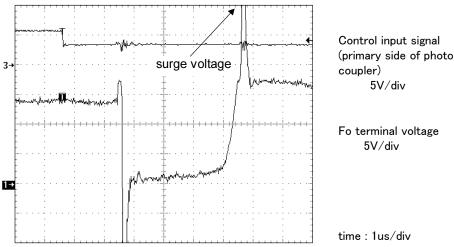

Depending on the pattern layout of Fo, surge voltage over 20V is sometimes observed at the Fo terminal. Due to this surge voltage, the electric strength is exaggerated and the LED part of the photo-coupler destroys. Be careful of the pattern layout. If the surge voltage is difficult to be reduced, add a diode in the converse and parallel(It refers to p1). To make low-impedance is important.

Fig.9.3 The example of the extraordinary waveform of the Fo terminal

#### (5) Example of photo coupler

The example of the photo-coupler recommended for IPM is shown below.

#### High speed photo coupler

High speed photo couplers are connected to the control input terminals of IPM.

When choosing photo coupler, pay attention to the parameters of response time (tpLH,tpHL) and CMR.

Choose the photo coupler that the value of tpLH,tpHL is less than 0.8us, and with high CMR.

Especially, ensure that the phenomena such as the ringing not occur.

For example)

PS9613 (NEC)

TLP559(IGM) (Toshiba)

The photo-coupler manufacturer sometimes has the IPM exclusive-goods ( another form name ) which sorted out a characteristic. Please inquire the photo-coupler of IPM compatible for the malfunction prevention when order.

## Low speed photo coupler

Low speed photo coupler is connected Fo terminal of IPM.

When choosing photo coupler, pay attention to the parameter of CTR.

Choose the photo coupler that the value of CTR is equal to or more than 100 %.

For example) TLP-521 (Toshiba) PS2502 (NEC)

Please inquire the manufacturer that the photo-coupler has or has not problem when work under your environmental condition.

## Words and terms)

CTR (Current Transfer Ratio) : The ratio of the output current to the input current CMR (Common Mode Rejection) : The maximum rise ratio of common mode voltage tpLH,tpHL : The Propagation delay time  $L\rightarrow H,H\rightarrow L$

Fig.9.4 The example of the input/output waveform of the control input terminal(photo coupler output).

## (6) Notice of using photo coupler

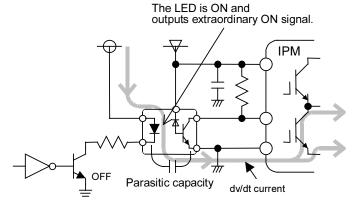

The photo coupler can isolate the primary side and secondary side. But, this is not correct at the high frequency. Because, photo coupler have a parasitic capacity between primary side and secondary side. When high dv/dt is impressed, the pulse electric current flows from the primary side to the secondary side via the parasitic capacity of photo coupler. This current sometimes turn on the photo coupler.

Therefore, it is important to design a circuit so that the LED will not turn on erroneously by this dv/dt.

When the input signal is OFF, make sure the circuit that the LED of primary side of photo coupler is with low-impedance.

Fig.9.5 The example of the circuit which isn't good

Fig.9.6. The example of the circuit to recommend

The recommended circuit doesn't make malfunction (LED of primary side of photo coupler is ON) because the dv/dt current can not turn ON the LED of primary side of photo coupler.

Please consult the application-note of the photo coupler for the detailed instruction of the circuit around the photo coupler.

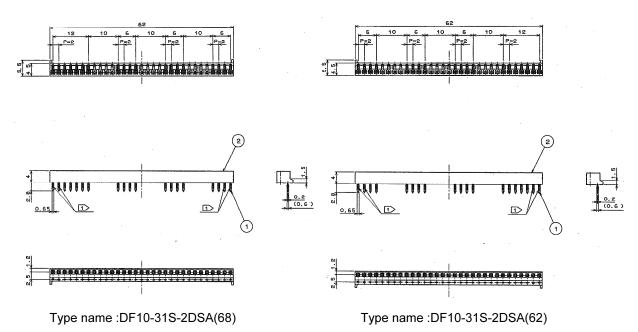

## (7) Connecter for control terminal of IPM

We use the connector from "HIROSE ELECTRIC CO., LTD" in our test of IPM. The following connector is recommended. The pace of this connector is 2.00 mm. It is the special connector of IPM which secured an electrical clearance among the terminals (U-V,V-W,W-U of P-side and N)

The terminal with gold plate is recommended from the viewpoint of contact reliability.

The details of the connector inquire of the manufacturer (HIROSE ELECTRIC CO., LTD.).

#### Note)

In the B4LB/B5LB/B6LB type, installation by solder is being recommended by the printed circuit board and the input and main terminal.

## (8) The material of control terminal of IPM (B4LA / B5LA / B6LA type)

As a reference of the connector selection, the material and the metal finishing of the control terminal on the side of IPM are shown below.

| Main material     |           | Brass       | _                           | → |

|-------------------|-----------|-------------|-----------------------------|---|

| The specification | substrate | Nickel (Ni) | Thickness _<br>= 1 ~ 5µm    | H |

| of the plating    | surface   | Gold(Au)    | Thickness<br>= 0.05 ~ 0.2µm |   |

#### (9) The guide pin of IPM

The guide pin on both sides of the control terminal of IPM is metal. The guide pin is molded by plastic, and isolated.

In the B4LB / B5LB / B6LB  $\,$  type, installation by solder is being recommended,  $\,$  the plating of control terminal for these types are Sn  $\,$

## 9-3 Control Power supply of IPM

#### (1) The control power supply

The voltage range including ripples should meet the specification.

| Control supply voltage V <sub>D</sub> (V) | Operation behavior                                                                                                                                                                                                        |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0~4.0                                     | It is almost the same as no power supply.  External noise may cause IPM malfunction (turns ON).  Supply under-voltage protection will not operate and no Fo signal will be asserted.                                      |

| 4.0~12.5                                  | Even if control input signals are applied, IGBT does not work Supply under-voltage protection starts operation and outputs Fo signals.                                                                                    |

| 12.5~13.5                                 | Switching operation works. However, this value is below the recommended one, $V_{\text{CE(sat)}}$ and switching time will be out of the specified values, it may increase collector dissipation and junction temperature. |

| 13.5~16.5                                 | Recommended values.                                                                                                                                                                                                       |

| 16.5~20                                   | Switching operation works. This range, however, is over the recommended value, thus, too fast switching speed might cause the chips to be damaged                                                                         |

| 20.0~                                     | The control circuit will be destroyed.                                                                                                                                                                                    |

## Specifications for Ripple Noise

High frequency noise super imposed on the control IC supply line might cause IC malfunction and cause an Fo signal output, and results IPM stop (interrupt gates). To avoid such malfunction, the supply circuit should be designed such that the noise fluctuation is smaller than +/- 5V/us, and the ripple voltage is less than 2V.

Specification:

$$\frac{dv}{dt} \le \pm 5V/us$$

,  $Vripple \le 2Vp - p$

When the noise on the power supply line is a high frequency(pulse-width<about 50ns, pulse-vibration<about 5V) which does not cause an Fo output from IPM, the noise can be ignored.

The power supply should be a low impedance, be careful of the pattern layout.

Connect a bypass condenser with good frequency response and a smoothing condenser close to the terminals of IPM. It is effective for the prevention of the malfunction.

#### Control Supply Starting up and Shutting Down Sequence

Control supply V<sub>D</sub> should be started up prior to the main supply (P-N supply). Control supply V<sub>D</sub> should be shut down after the main supply (P-N supply).

If the main supply had been started up before the control supply, or if the main supply remains after control supply was shut down, external noise might cause the IPM malfunction.

As for the P-side, use the control power supply which was insulated in each of all of the 2 aspects. As for the N-side, because the GND in 2 aspects and the converter part is common, a common power can be used for the three control sources in amount.

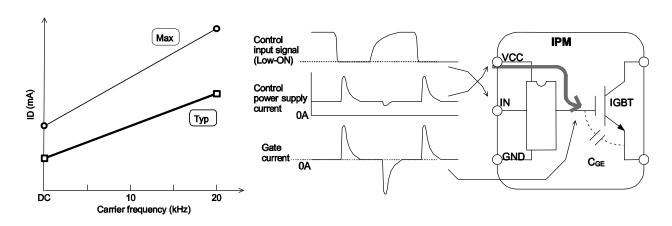

## (2) The circuit current of control power supply of IPM

The circuit current of control power supply of IPM is shown below. This current is average of DC and fc=20kHz.

Condition: VD=15V,Tj=25 deg C,Unit: mA

| PV-IPM          | N-side |     |       |     | P-side |     |       |     |

|-----------------|--------|-----|-------|-----|--------|-----|-------|-----|

|                 | DC     |     | 20kHz |     | DC     |     | 20kHz |     |

| Type Name       | Тур    | Max | Тур   | Max | Тур    | Max | Тур   | Max |

| PM 50B4LA/LB060 | 10     | 20  | 28    | 38  | 5      | 10  | 12    | 17  |

| PM 50B5LA/LB060 | 15     | 25  | 34    | 46  | 5      | 10  | 12    | 17  |

| PM 50B6LA/LB060 | 20     | 30  | 4 1   | 56  | 5      | 10  | 12    | 17  |

| PM 75B4LA/LB060 | 15     | 25  | 46    | 62  | 6      | 12  | 16    | 22  |

| PM 75B5LA/LB060 | 20     | 30  | 56    | 76  | 6      | 12  | 16    | 22  |

| PM 75B6LA/LB060 | 24     | 34  | 65    | 88  | 6      | 12  | 16    | 22  |

The circuit current of the IPM control power supply at other frequency

The circuit current of control power supply of IPM increases with the carrier frequency.

The carrier frequency dependence of the circuit current of the IPM control power supply can be approximated as a straight line like the following figure.

The gate of IGBT used in IPM has an input-capacitance(Cies=C<sub>GE</sub>+C<sub>CG</sub>).

The current to be charged and discharged by flowing through the gate at the timing of gate on and off.

There is IPM that this current becomes 1~2 A.

When IPM is turn-off, the dv/dt current from the collector of IGBT flows into the side of the control power supply. Design a control power supply in the low impedance so that this dv/dt current can be absorbed. Otherwise, The control IC of IPM might make malfunction and On signal is activated by this current resulting arm short circuit.

The control power supply circuit needs a capacity that it can supply and absorb these current. Usually, such problems(maximum current, impedance) can be avoided by power supply circuit and also bypass ,smoothing condenser. But, the effect of the condenser is influenced by the inductance of the wiring pattern. Determine the condenser capacity after verifying the substrate and the equipment.

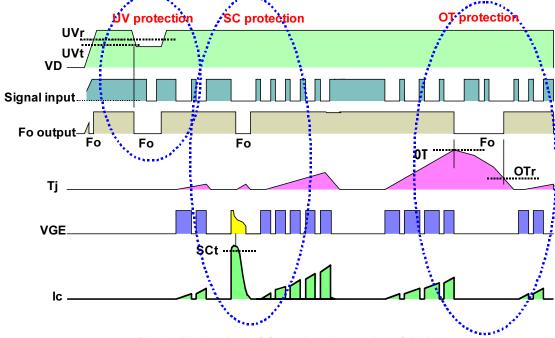

## 9-4 Fault Signal of IPM

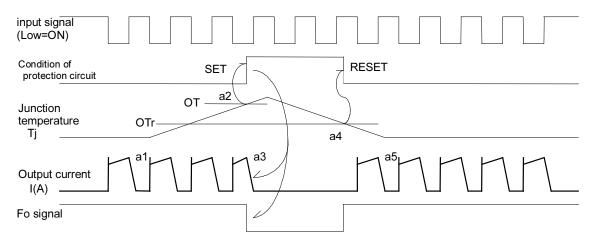

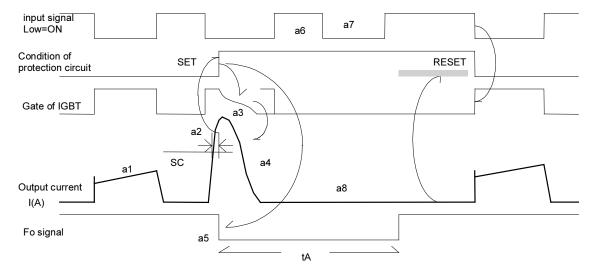

IPM (Intelligent Power Modules) have sophisticated built-in protection circuits that prevent the power devices from being damaged should the system malfunction or be over stressed. Control supply under-voltage(UV), over temperature(OT), and short-circuit(SC) protection are all provided by the IPM's internal gate control circuits. A fault output signal is provided to alert the system controller if any of the protection circuits are activated. Following Fig.9.7 is a block diagram showing the IPMs internally integrated functions.

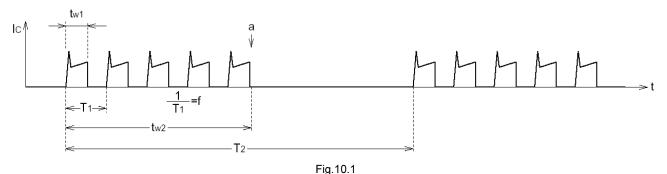

Fig.9.7 Timing chart of Control and protection of IPM

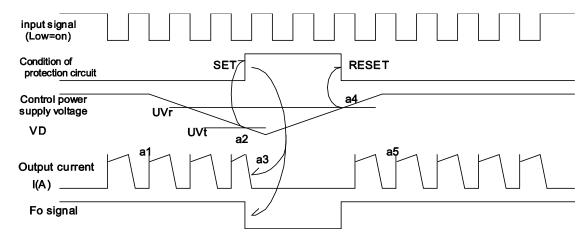

#### Control Supply Under-Voltage (UV)

The IPM's internal control circuits operate from an isolated 15V DC supply. If, for any reason, the voltage of this supply drops below the specified under-voltage trip level (UVt), the power devices will be turned off and a fault signal will be generated. Small glitches less than the specified tdUV(<10us) in length will not affect the operation of the control circuitry and will be ignored by the under voltage protection circuit. In order for normal operation to resume, the supply voltage must exceed the under voltage reset level (UVr). Operation of the under-voltage protection circuit will also occur during power up and power down of the control supply. This operation is normal and the system controller's program should take the fault output delay (tfo) into account.

#### Note:

- 1. Application of the main bus voltage at a rate greater than 20V/ms before the control power supply is on and stabilized may cause destruction of the power devices.

- Voltage ripple on the control power supply with dv/dt in excess of 5V/us may cause a false trip of the UV lock-out.